- 全部

- 默认排序

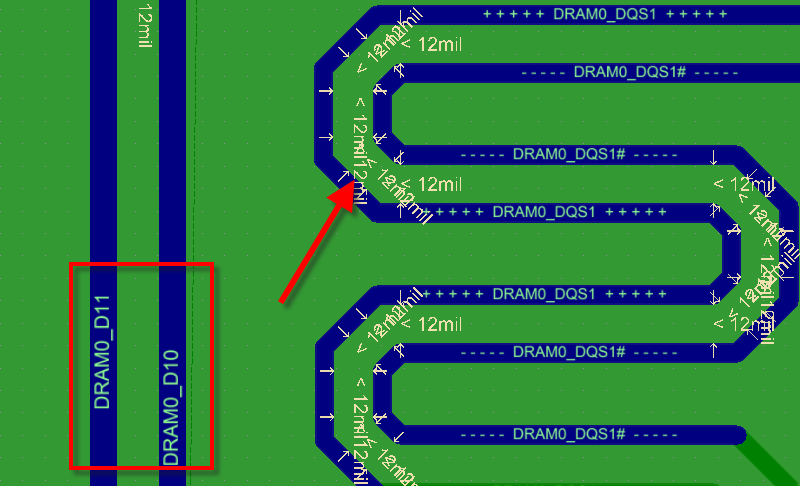

我们在用allegro进行PCB设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。

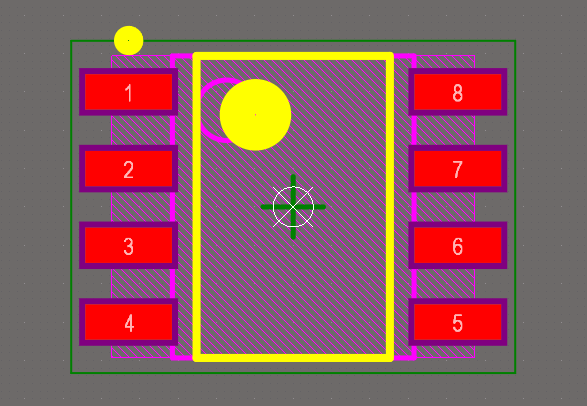

我们知道作为PCB设计工程师我们在进行PCB设计之前都需要进行PCB封装的创建,但是对于一些新手工程师对于创建的封装的精准数据无法进行判断,并且对一些焊盘的补偿参数不是很明白,导致自己做出的封装只能满足打样或者无法使用的囧状。

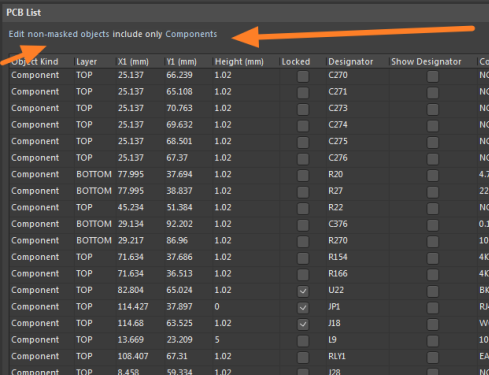

我们来认识一下,这个是我们的PCBlist界面,当我们选中我们的器件的时候,我们上面有两个选择,当我们需要对应的器件的参数进行修改的时候,我们进行我们对应的器件的参数进行对应的一个个进行修改,

关于PCB设计中晶体晶振的布局和布线要求,布局要求:1、布局整体紧凑,一般放置在主控的同一侧,靠近主控IC。2、布局是尽量使电容分支要短(目的:减小寄生电容,)

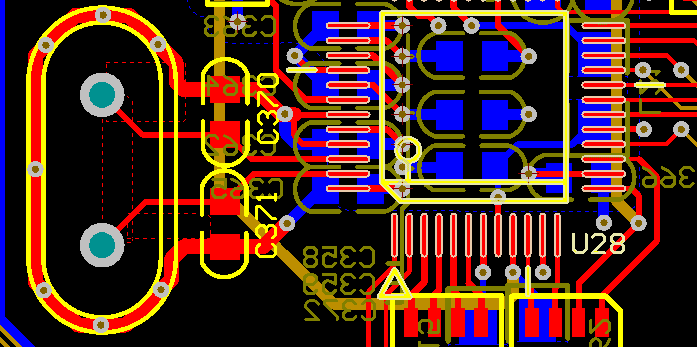

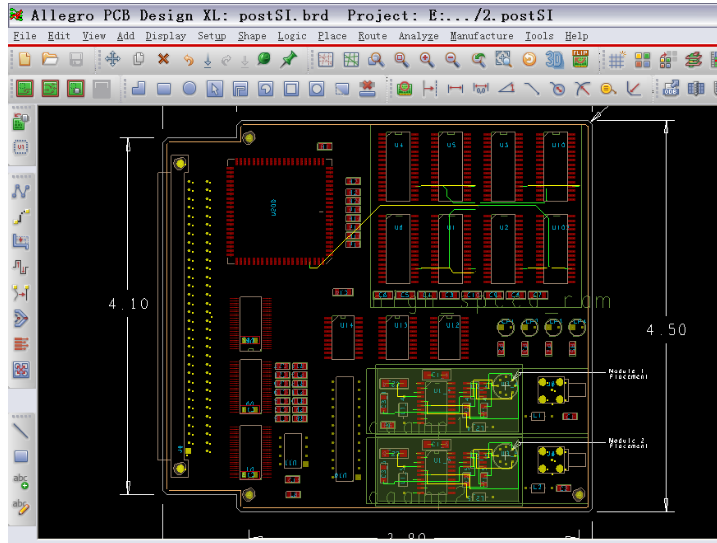

PCB的相同模块如图12-10所示。很多PCB设计板卡中存在相同模块,给人整齐、美观的感觉。从设计的角度来讲,整齐划一,不但可以减少设计的工作量,还保证了系统性能的一致性,方便检查与维护。相同模块的布局布线存在其合理性和必要性。

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

爬电距离:沿绝缘表面测得的两个导电零部件之间或导电零部件与设备防护界面之间的最短路径。 电气间隙:在两个导电零部件之间或导电零部件与设备防护界面之间测得的最短空间距离。即在保证电气性能稳定和安全的情况下,通过空气能实现绝缘的最短距离。

电子产品设计的基本流程包括项目启动,市场调研,项目规划,项目详细设计,原理图设计,PCB布局、布线,PCB制板、焊接,功能、性能测试等环节,我们在教学过程中,一般按下面的步骤进行电子产品设计:第一步:获取产品需要实现的功能;

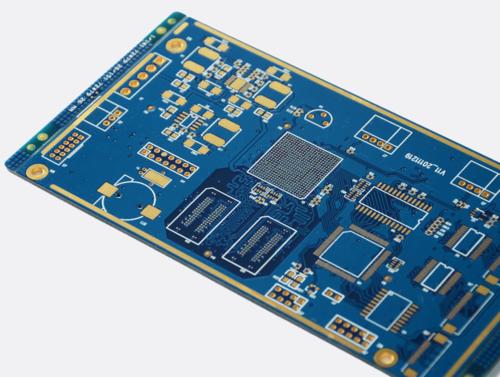

高速高密度多层PCB板的SI/EMC(信号完整性/电磁兼容)问题长久以来一直是设计者所面对的最大挑战。然而,随着主流的MCU、DSP和处理器大多工作在100MHz以上(有些甚至工作于GHz级以上),以及越来越多的高速I/O埠和RF前端也都工作在GHz级以上,再加上应用系统的小型化趋势导致的PCB空间缩小问题,使得目前的高速高密度PCB板设计已经变得越来越普遍。许多产业分析师指出,在进入21世纪以后,80%以上的多层PCB设计都将会针对高速电路。

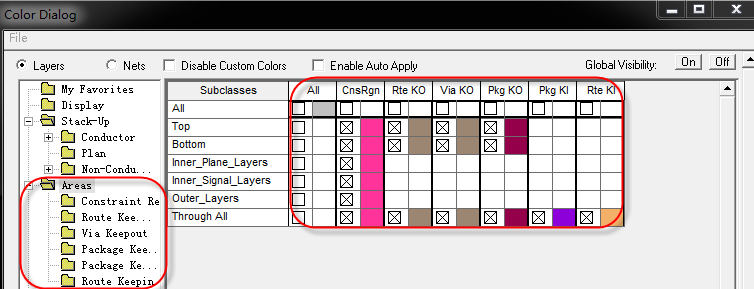

我们在进行PCB设计的时候,需要根据不同的PCB板结构以及一些电子产品的需求来进行各种不同区域的设计,包括允许布局区域设计、禁止布局区域设计。允许布线区域设计等等。在Allegro设计中,设置这些就在Areas,如图5-60所示。 图5-60 各类布局布线区域示意图Ø 在Allegro软件中有Route Keepout、Route Keepin、Package Keepout、Package Keepin、Via Keepout等多种类型的区域进行设置,对PCB工

扫码关注

扫码关注